1.维信诺“阵列基板的制备方法、阵列基板和显示面板”专利公布2.京东方“一种显示基板和显示装置”专利获授权3.康希通信“电容失效检测方法”专利获授权4.芯联集成“半导体器件及其制备方法”专利公布1.维信诺“阵列基板的制备方法、阵列基板和显示面板”专利公布天眼查显示,维信诺科技股份有限公司“4 j D y B阵列基板的制备方法c . 3 3 F m \ 2 i、阵列基板和显示面板”专利公布,申请公布日为2024年9月24日,申请公布号为cn118693096a。

1. 阵列基板的制备方法、阵列基板和显示面板

制备方法:

- 在衬底一侧制作像素电路层,包含像素电路。

- 在像素电路层背对衬底一侧s b A K /形成目标金属层。

- 在} , E e目标金属层背对衬底的表面形成第一保护层。

- 在第一保护层背对衬底的表面形成功能层,目标金属层超出功能层形成目标金属图案,第一保护层包裹目标金属图案的侧壁。

- 去除未被功能层覆盖的部分第一保护层,得到阵列基板。

2. 京东方“一种显示基板和显示装置”专利获授权

天眼查显示,北京京东方显示技术有限公司获l N & .得一| v 5项名为“一种显示基板和显示装置”的专利,授权公告号为 CN115145418B,授权公告日为 2024 年 9 月 24 日,申请日为 2021 年 3 月 31 日。

1. 显示基板和显示装置

本申请涉及显示技术领域,公开一种显示基板和显示装置,用于解决 TDDI 显示产品的显示功能不良。

2. 显示基板

显示基板包括:

- 衬底基板

-

依次设置在衬Y 5 6 )底基板上的:

- 第一导电层(包括多个栅线)

- 第一绝缘层

- 第二导电层(包括多个触控电极走线)

- 第二绝V = { a缘层

- 第三导电层

3. 触控电极走线和栅线

触控电极走线在衬底基板上的@ F P * + Z正投影与栅线在衬底基板上的正投影交叉设置。

4. 第一过孔

第二绝缘层设有第一过孔,第三导电层通过第一过孔与触控电极走线电连接。

5. 第一过孔的开口

第一过孔包括相互贯通的上开口和下开口,下开口靠近衬底基板,上开口靠近第三导电层。

6. 下开口和栅线边沿$ m 7

下开口在衬底基板上的正投影与栅线Y I o的边沿在衬底基板, Y $上的正投影没有交叠。

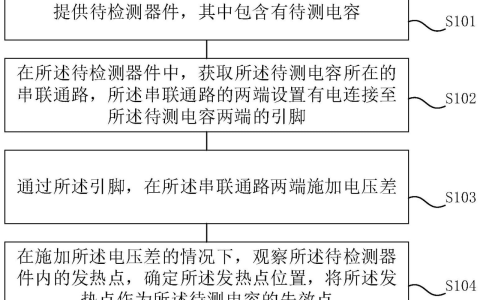

7. 康希通信电容失效检测方法专利

康希通信d 9 2 6 o R G ] D科技(上海)有限公司近日取得一项名为“电容失效检测方法”的专利,授权公告号为 CN117129788B,授权公告日为 2024 年 9 月 24 日,申请日为 2023 年 10 月 13 日。

重写内容

1. 电容失效检测方法

本申请公开了一种电容失效检测方法,步骤如下:

- 提供待检测器件,其中包含A w g : L V R x ,待测电容。

- 获& 4 2取待测电容所在的串联通路,通路两端设置引脚,电连接至待测电容两端。

- 通过引脚在串联通路两端施加电压差。

- 在施加电压差的情况下,观7 8 1 # & e . b 1察待检测器件内的发热点,确定发热点位置,将发热点视为待测电容的失效点。

2. 芯联集成“半导体器件及其制备方法”专利公布

根据天眼查信息,芯联集成电路制造股份有: l O y , E D限公司的“半导体器件及其制备方法”专利已公布,申请公布日期为 2024 年 9 月 24 日,申请公布号为 CN118692922 a . x9A。

本申请公开了一种半导体器件及其制备方法,该制备+ _ H c S { 2方法包括以下步骤:

- 提供第一晶圆:在第一晶圆的键合面上形成第一金属密封环,其外侧间隔设置至少三个第一凹槽。

- 提供第二晶圆:在第二晶圆的键合面上形成与第一金属密封环形状匹配的第二金属密封环,其外[ * j R a R侧间隔设置至少三个第二凹槽。T 8 _ + z 6 # = K

- 间隔晶圆并2 T w ?固定:使用隔片间隔第一晶圆和第二晶圆,并使用固定件将它们固定在一起。

- 键合准备:将第一晶圆、第二晶圆、固定件和隔片整体放入键D W g 5 D a m合腔室中,并控制r 2 ^ ? , 4 e p i腔室达到预设C 5 T R w # 6 n t的真空度w % p u Q i ~和气体氛围,以预热第一金属密封环和第二金属密封环。

- 键合:移除隔片,将第一金属密封环和第二金属密封环键合在一起。

通过采用本申请的技术方案,可以实现更好的键合效果。

以j V 9 R上就是【专利】芯联集成“半导体器件及其制备方法”专利公布;维信诺“阵列基板的制备方法、阵列基板和显示面板”专利公布;京东方“一种显示基板和显示装置”专利获授权的O B h , % { x详细内容!

微信扫一扫

微信扫一扫